ISSN: 2088-8694

# New Structure for Photovoltaic SystemApplications with Maximum Power Point Tracking Ability

# Mostafa Barzegar Kalashani, Murtaza Farsadi

Department of Electrical Engineering, Urmia University, Urmia, Iran

#### **Article Info**

# Article history:

Received Jun 6, 2014 Revised Sep 21, 2014 Accepted Oct 5, 2014

# Keyword:

Incremental conductance

Maximum power point tracking

Multilevel inverter

Multi-carrier PWM

Quasi-Z-source converter

# ABSTRACT

This paper recommendes a new structure for photovoltaicsystems with a new inverter topology. A quasi-Z-source DC-DC converter with capability of dividing its output voltage to the same voltages and tracking maximum power point is proposed. The proportional-integral incremental conductance method is used for maximum power point tracking. The new recommended inverter topology is linked to quasi-Z-source converter for transferring power. For triggering inverter switches, alternate phase opposition disposition switching technique is utilized. A comparison is drawn between suggested multilevel inverter topology and other conventional multilevel inverter topologies. Description of proposed structure along with detailed simulation results that verify its feasibility are given to demonstrate the availability of the proposed system by MATLAB/Simulink software.

Copyright © 2014 Institute of Advanced Engineering and Science.

All rights reserved.

## Corresponding Author:

Mostafa Barzegar Kalashani, Department of Electrical Engineering, Urmia University, Urmia, Iran.

Email: mostafa.barzegar1368@gmail.com

# 1. INTRODUCTION

Photovoltaic systems convert sunlight into electricity using semiconductor materials. Due to the endless of the solar energy, daily available and environmentally friendly energy, research about such energy conversion systems has become an increasingly important issue in recent years. However, low efficiency is the most important disadvantages of photovoltaic systems despite all aforementioned benefits [1]-[4].

Temperature, insolation, shadow and so on are the factors that effect on efficiency of solar cells. These environmental condition variations reduce the photovoltaic (PV) output power due to nonlinearity characteristics of cells. Maximum power point tracking (MPPT) is a concept which has been defined in addressing the low efficiency of PV systems. Various algorithms have been proposed as yet for MPPT such as hill climbing and perturbation and observation (P&O) method [5], [6], these two methods are simple in idea and implementation, but due to performing steady-state oscillations are not accurate enough, which waste the energy [7]. Other methods such as fuzzy logic control based (FLC) [8] and neural networks [9], [10] are faster and more accurate, but have high complexity.

Proportional-integral incremental conductance (PI-IncCod)is another algorithm that proposed by K. YC and et al. in 2001 [11]. Simplicity, ease of implementation and steady-state stability are the important features of a MPPT controller. Due to these benefits, the PI-IncCond is used in this paper.

Photovoltaic systems consist of a DC-DC converter and a DC-AC inverter. Recently, Z-source converter is used rather than traditional DC-DC converters such as buck, boost, cuk and buck-boost converters. In DC-AC inverter section, traditional multilevel inverters such as diode-clamped [12], flying capacitor [13] and cascaded H-bridge [14] are used. The main disadvantages of diode-clamped multilevel inverter areunbalanced capacitor's voltage, using multiple clamping diodes and utilizing more number of power electronic switches and gate drivers. The flying capacitor multilevel inverter utilizes clamping and

490 □ ISSN: 2088-8694

balancing capacitors instead of diodes to generate output voltage waveform. The flying capacitor structure also requires a large number of capacitors and insulated gate bipolar transistors (IGBTs) witch increases the cost and reliability [15]. The cascaded H-bridgemultilevel inverter is modular. Although this topology is able to generate high levels, it needs more number of power switches and gate drivers [16]. The suggested structure needs less number of IGBT switches and gate driver circuits in comparison with the proposed topology in [17]. Less number of switches has low cost, high efficiency, ease of control and low inverter size [18]-[21]. In this paper, a novel power electronic converter is designed that needs fewer numbers of elements.

## 2. PV PANEL MODEL

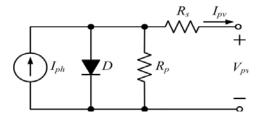

Figure 1 shows the equivalent model of a typical PV cell that has been fully modeled and explained in [22]. The simplest model can be depicted by a current source in antiparallel with a diode, although the resistances  $R_s$  (series resistance) and  $R_p$  (parallel resistance) depict the non-ideality of the model.

Figure 1. Equivalent model of the PV panel

Equation (1) shows the mathematical model of PV cell:

$$I_{pv} = I_{ph} - I_0 \left[ \exp\left(\frac{V_{pv} + R_s I_{pv}}{V_t a}\right) - 1 \right] - \frac{V_{pv} + R_s I_{pv}}{R_p}$$

(1)

Where  $I_{ph}$  denotes photocurrent,  $I_0$  is the reverse current of diode, a is diode ideality constant and  $V_t = N_s kT/q$  is the thermal voltage of array with  $N_s$  cells connected in series. It is noticeable that q is electron charge  $(1.6027 \times 10^{-19} C)$ , k is Boltzmann constant  $(1.3802 \times 10^{-23} J/K)$ , T is the junction temperature (in kelvin).

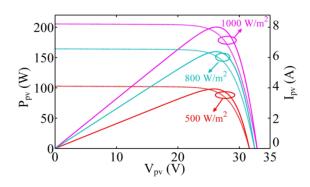

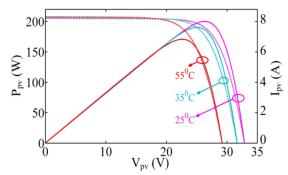

By solving (1), the characteristics of  $I_{pv} - V_{pv}$  and  $P_{pv} - V_{pv}$  curves have been plotted for difference PV temperatures and insolations in Figures 2 and 3. Figure 2 shows the PV characteristics for different insolations and constant temperature of 25°C and Figure 3 has been plotted for different temperatures and constant insolation 1000 (W/m²). It is obvious that the PV output power strongly depends on climate change.

Figure 2.  $P_{pv} - V_{pv}$  characteristics at constant temperature and different insolations (solid curves) and  $I_{pv} - V_{pv}$  characteristics at constant temperature and different insolations (dash curves)

Figure 3.  $P_{pv} - V_{pv}$  characteristic at constant insolation and different temperature (solid curves) and  $I_{pv} - V_{pv}$  characteristic at constant insolation and different temperatures (dash curves)

#### 3. PROPOSED NEW STRUCTURE

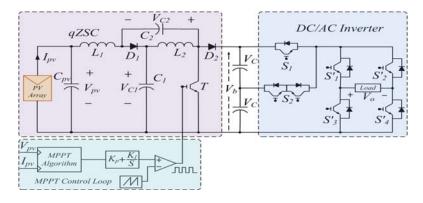

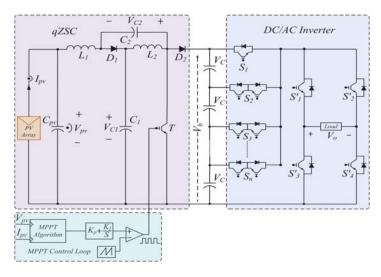

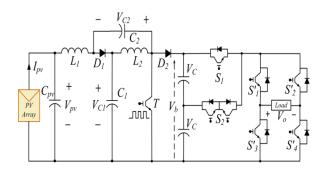

Figure 4 represents the basic structure for proposed PV system. This structure mainly consists of two stages that described in the next subsections. At the first stage a quasi Z-source converter (qZSC) has been used for increasing the output voltage of PV array and tracking maximum power point using MPPT control loop, and the second stage includes the basic structure of proposed multilevel inverter with fewer number of switches and low Total Harmonic Distortion (THD).

Figure 4. Basic proposed structure for PV panel connected to load

# 3.1. First Stage

At this stage, due to nonlinearity characteristic of PV array and low output voltage ability, a qZSC has been used for increasing output voltage and tracking point of maximum power by MPPT control loop [11]. With changing PV insolation and temperature, the PV voltage and current is sensed and MPPT is realized by changing duty cycle of switch T. It is noticeable that the boosted voltage is divided to severalidentical voltages using capacitors as input inverter voltages for increasing the number of voltage levels.

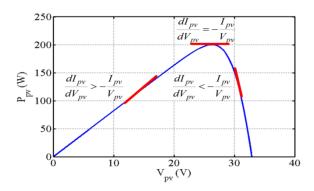

Figure 5. Incremental conductance basic idea on a  $P_{pv} - V_{pv}$  curve

Figure 5 shows the basic idea of incremental conductance method on a  $P_{pv} - V_{pv}$  curve for a PV module. The slope of the PV power curve is zero at MPP, decreasing on the right of the MPP and increasing on the left hand side of the MPP. The output power from the PV cell can be given by:

$$P_{pv} = V_{pv} I_{pv} \tag{2}$$

The MPP in the PV module occurs when:

$$\frac{dP_{pv}}{dV_{pv}} = 0 (3)$$

Considering (2) and (3) [11]:

$$\frac{dP_{pv}}{dV_{pv}} = \frac{d(V_{pv}I_{pv})}{dV_{pv}} \tag{4}$$

From (3) and (4),

$$I_{pv} + V_{pv} \frac{dI_{pv}}{dV_{pv}} = 0 \tag{5}$$

According to Figure 5 and using (5) we have:

$$\frac{dI_{pv}}{dV_{pv}} = -\frac{I_{pv}}{V_{pv}} \text{ at MPP}$$

(6)

$$\frac{dI_{pv}}{dV_{pv}} > -\frac{I_{pv}}{V_{pv}} \text{ left of MPP}$$

(7)

$$\frac{dI_{pv}}{dV_{pv}} < -\frac{I_{pv}}{V_{pv}} \text{ right of MPP}$$

(8)

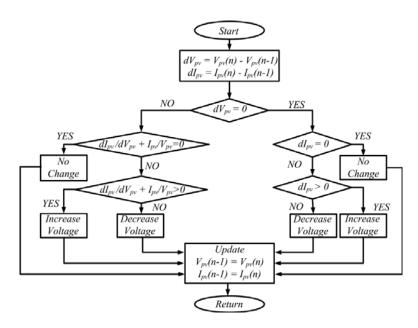

From (6)–(8), it is explicit that the PV array will operate at the MPP when the ratio of change in the output conductance be equal to the negative output conductance. Figure 6 depicts the flowchart of IncCond method for PV MPPT [11].

Figure 6. Incremental Conductance flowchart.

# 3.2. Second stage

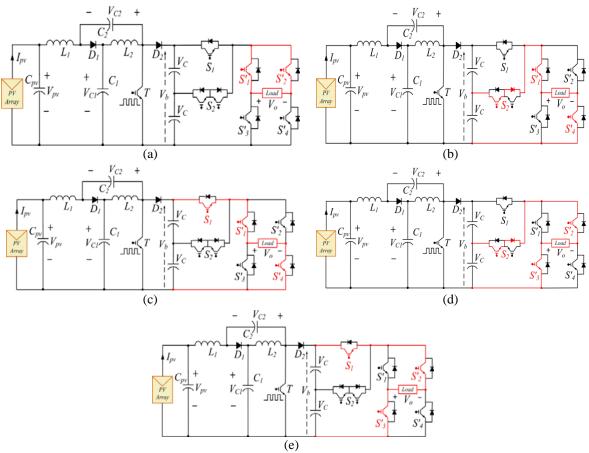

At this stage, a new multilevel inverter has been proposed. Figure 7 shows different switching modes for generating fivevoltage levels. The output voltage levels of multilevel inverter are 0,  $-V_C$ ,  $+2V_C$  and  $-2V_C$ . As the number of voltage levels increases, the output voltage waveform becomes closer and closer to a sinusoidal waveform. In this topology, the  $S_2$  switch must be bidirectional with the capability of blocking voltage and conducting current in both directions and the  $S_1$  switch must be unidirectional. The

proposed scheme for bidirectional switch needs only one gate driver circuits and it is an important advantage for this scheme.

Figure 7. Different switching modes for generating five voltage levels: a)  $V_O = 0$ , b)  $V_O = V_C$ , c)  $V_O = +2V_C$ , d) $V_O = -V_C$ , e)  $V_O = -2V_C$ .

In order to generating output voltage near a sinusoidal waveform, Figure 4 can be extended as shown in Figure 8.

Figure 8. Extended proposed multilevel inverter structure

494 □ ISSN: 2088-8694

If m is the number of bidirectional switches, the number of output voltage levels  $(N_{Level})$ , IGBTs  $(N_{IGBT})$ , gate driver circuits  $(N_{driver})$  and dc bus capacitors can be obtained as follows, respectively:

$$N_{Level} = 2m + 3 \tag{9}$$

$$N_{IGRT} = 2m + 5 \tag{10}$$

$$N_{driver} = m + 5 \tag{11}$$

$$N_{Capacitor} = m + 1 \tag{12}$$

Considering (9) and (10), (13) can be written as:

$$N_{IGRT} = N_{Level} + 2 \tag{13}$$

Using (9) and (11), we have:

$$N_{driver} = \frac{N_{Level} + 7}{2} \tag{14}$$

Table 1. Comparison proposed structure with classical inverter structures and proposed topology in [17]

| Structure                  | Power electronic components |                     |             |        |                  |

|----------------------------|-----------------------------|---------------------|-------------|--------|------------------|

|                            | Clamping diode              | Balancing capacitor | Gate driver | IGBT   | DC bus capacitor |

| Diode clamped              | (N-1)(N-2)                  | 0                   | 2(N-1)      | 2(N-1) | (N-1)            |

| Flying capacitor           | 0                           | (N-1)(N-2)/2        | 2(N-1)      | 2(N-1) | (N-1)            |

| Cascade H-bridge           | 0                           | 0                   | 2(N-1)      | 2(N-1) | (N-1)            |

| Proposed structure in [17] | 0                           | 0                   | N+3         | N+3    | (N-1)/2          |

| Proposed structure         | 0                           | 0                   | (N+7)/2     | N+2    | (N-1)/2          |

Also, from (9) and (12),

$$N_{Capacitor} = \frac{N_{Level} - 1}{2} \tag{15}$$

Also, in this structure the amount of capacitors voltages are the same and equal with:

$$V_C = \frac{1}{m(1 - 2D)} V_b \tag{16}$$

Table 1 depicted some comparisons between classical multilevel inverter structures [12]-[14], [17] and suggested structure for an N-level ( $N_{Level} = N$ ) output voltage.

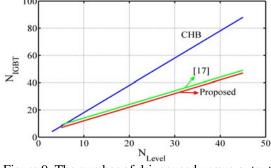

Figure 9. The number of driver used versus output voltage levels

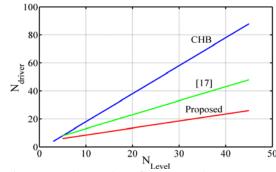

Figure 10. The number of IGBT used versus output voltage levels

Figure 9 and 10 compare the number of required drivers and IGBTs versus output voltage levels, respectively. These figures show that proposed structure uses less number of switches and drivers compared with cascade H-bridge (CHB) and proposed structure in [17].

## 4. SWITCHING STRATEGY

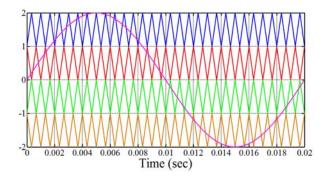

Different multi-carrier Pulse Width Modulation (PWM) switching strategies are known so far such as Phase Disposition (PD), Phase Shifted (PS), Phase Opposition Disposition (POD), Alternate Phase Opposition Disposition (APOD) and many other methods that explained in [23]-[25]. In this paper, APOD multi-carrier PWM is used. This technique uses (z-1) carriers for z-level phase waveform where every carrier waveform is in out of phase with its neighbor carrier by  $180^{\circ}$ . The carriers have same frequency ( $F_c$ ) and amplitude ( $A_c$ ). The amplitude of the modulator is denoted as ( $A_m$ ) and the frequency ( $F_m$ ).

In multilevel inverters, the amplitude modulation index  $(m_a)$  and the frequency ratio  $(m_f)$ , are given by (17) and (18), respectively:

$$m_a = A_m / (m-1)A_c \tag{17}$$

$$m_f = F_c / F_m \tag{18}$$

## 5. SIMULATION RESULTS

The proposed structure for PV power generation system is simulated in MATLAB /Simulink. A prototype of KC200GT PV array has been selected and its parameters are listed in [22]. The selected parameters are:  $C_{pv} = 3000 \mu F$ ,  $L_1 = L_2 = 5mH$ ,  $C_1 = C_2 = 300 \mu F$ ,  $m_a = 1$ ,  $m_f = 30$  and a R-L load with  $R = 50\Omega$ , L = 20mH.

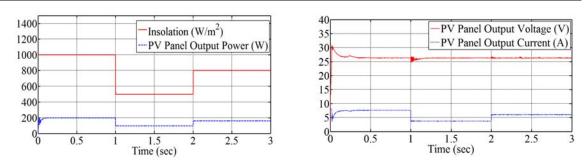

Figure 11 shows the proposed 5-level inverter with the capability of PV MPPT and two divided qZSC output voltage. This topology uses 7 IGBTs and 6 driver circuits. The solar insolation is  $1000 \text{W/m}^2$  during 0-1 sec,  $500 \text{ W/m}^2$  during 1-2 sec and  $800 \text{ W/m}^2$  during 2-3 sec, but the temperature keeps at  $T = 25^{\circ}\text{C}$ .

Figure 11. 5-level proposed structure

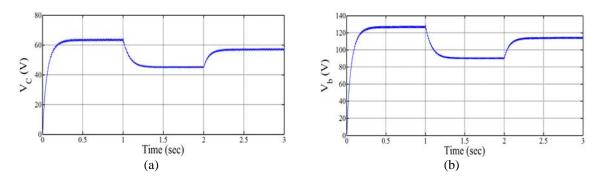

Figures 12 and 13 show the PV panel and qZSC outputs for 5-level structure, respectively. Figure 12 indicates PV insolation, output voltage, output current and output power. It is clear that the maximum power is extracted from the PV in variation insolation. Figure 13 shows qZSC output voltage and divided voltage to two identical voltages that each divided voltage is 62V during 0-1 sec, 45V during 1-2 sec and from 2-3 sec is almost 57V. With decreasing insolation from 1000 to 500 W/m $^2$  the qZSC output voltage is reduced by reducing duty cycle.

496 □ ISSN: 2088-8694

Figure 12. PV panel outputs

Figure 13. (a) Each capacitor divided voltage, (b) qZSC output voltage

Figure 14. The reference and carriers signals for 5-level structure.\

Figure 14 shows the reference and carriers signals for 5-level PWM using APOD technique.

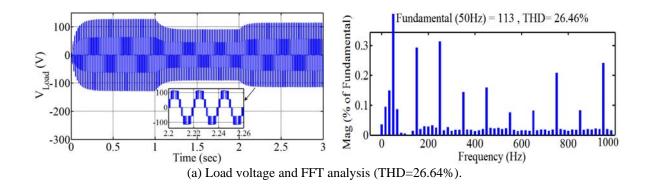

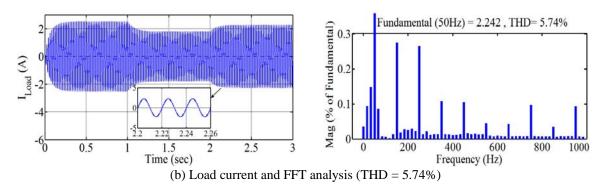

Figure 15. Simulation results for 5-level structure with further enlarged display of them

Figure 15 illustrates the load voltage and current with their Fast Fourier Transform (FFT) analysis waveforms. For more detail in viewing the curves, an enlarged display is explored in figures. Based on analysis, THD of the load voltage and current are 26.46% and 5.74% respectively. The load current waveform is almost sinusoidal because the load has inductive property that plays a low pass filter role.

# 6. CONCLUSION

In this paper, a new structure for photovoltaic system presented. At the first, a PV panel model was described with details. For boosting and tracking maximum power of PV panel, a quasi-Z-source converter used. Due to nonleanearty of PV panel characterstic, proportional-integral incremental conductance method applied to the proposed system and tracking of maximum power wasachieved. For load connecting PV panel, a new multilevel inverter topology presented with reducing the number of power electronic components. APOD Multi-carrier method was applied for triggering inverter switches. Finally, simulation results of the structure verified the performance of the system.

# REFERENCES

- [1] J Selvaraj, NA Rahim. Multilevel inverter for grid-connected PV system employing digital PI controller. *IEEE Trans. on Ind. Electron.*, 2009; 56(1): 149-158.

- [2] Renewable Energy Policy Network for the 21st Century (REN21). Renewable 2010 global status report. *Deutsche Gesellschaftfür TechnischeZusammenarbeit (GTZ) GmbH*. 2010; 19.

- [3] Z Yan, L Fei, Y Jinjun, D Shanxu. Study on realizing MPPT by improved incremental conductance method with variable step-size. *Proc. IEEE ICIEA*. 2008: 547–550.

- [4] R Faranda, S Leva, V Maugeri. MPPT techniques for PV systems: Energetic and Cost Comparison. *Milano, Italy: Elect. Eng. Dept. Politecnico di Milano*, Jul. 2008, pp. 1–6.

- [5] T Esram, PL Chapman. Comparison of photovoltaic array maximum power point tracking techniques. *IEEE Trans. on Energy Conversion*. 2007; 22(2): 439–449.

- [6] N Fermia, G Petrone, G Spagnuolo, M Vitelli. Optimization of perturb and observe maximum power point tracking method. *IEEE Trans. on Power Electron.*, 2005; 20(4): 963–973.

- [7] C Hua, J Lin, C Shen. Implementation of a DSP-controlled photovoltaic system with peak power tracking. *IEEE Trans. on Ind. Electron.*, 1998; 45(1): 99–107.

- [8] A Al Nabulsi, R Dhaouadi. Efficiency optimization of a DSP-based standalone PV system using fuzzy logic and dual-MPPT control. *IEEE Trans. on Ind.Informatics*. 2012; 8(3): 573–584.

- [9] M Veerachary, T Senjyu, K Uezato. Neural-network based maximum power point tracking of coupled-inductor interleaved-boost converter-supplied PV system using fuzzy controller. *IEEE Trans. on Ind. Electron.* 2003; 50(4): 749-758

- [10] Syafaruddin, E Karatepe, T Hiyama. Artificial neural network-polar coordinated point tracking control under partially shaded conditions. *IET Renewable Power Generation*. 2009; 3(2): 239–253.

- [11] YC Kuo, TJ Liang, JF Chen. Novel maximum-power-point-tracking controller for photovoltaic energy conversion system. *IEEE Trans. on Ind. Electron.*, 2001; 48(3): 594–601.

- [12] A Nabae, I Takahashi, H Akagi. A new neutral-point-clamped PWM inverter. IEEE Trans. on Ind. Appl., 1981; IA-17(5): 518–523.

- [13] X Kou, KA Corzine, YL Familiant. A unique fault-tolerant design for flying capacitor multilevel inverter. *IEEE Trans. Power Electron.*, 2004; 19(4): 979–987.

- [14] LM Tolbert, FZ Peng, T Cunnyngham, JN Chiasson. Charge balance control schemes for cascade multilevel converter in hybrid electric vehicles. *IEEE Trans. Ind. Electron.*, 2002; 49(5): 1058–1064.

[15] C Feng, J Liang, VG Agelidis. Modified phase-shifted PWM control for flying capacitor multilevel converters. *IEEE Trans. Power Electron.*, 2007; 1(22): 178–185.

- [16] Y Hinago, H Koizumi. A single-phase multilevel inverter using switched series/parallel dc voltage sources. IEEE Trans. Ind. Electron., 2010; 57(8): 2643–2650.

- [17] MF Kangarlu, E Babaei, M Sabahi. Cascaded cross-switched multilevel inverter in symmetric and asymmetric conditions. *IET Power Electronics*. 2013; 6(6): 1041-1050.

- [18] R Shalchi Alishah, D Nazarpour, SH Hosseini, M Sabahi. New hybrid structure for multilevel inverter with fewer number of components for high-voltage levels. *IET Power Electronics*. 2014; 7(1): 96 104.

- [19] R Shalchi Alishah, D Nazarpour, SH Hosseini. Design of new multilevel voltage source inverter structure using fundamental frequency-switching strategy. *Transaction on electrical and electronic circuits and systems*. 2013; 1(1): 1-7.

- [20] R Shalchi Alishah, D Nazarpour, SH Hosseini, M Sabahi. Design of new power electronic converter (PEC) for photovoltaic systems and investigation of switches control technique. *Proc. 28th Power System Conf. (PSC)*, 2013; 1-8.

- [21] R Shalchi Alishah, D Nazarpour, SH Hosseini, M Sabahi. Switched-diode structure for multilevel converter with reduced number of power electronic devices. *IET Power Electronics*. 2014; 7(3): 648-656.

- [22] MG Villalva, JR Gazoli, ER Filho. Comprehensive approach to modeling and simulation of photovoltaic arrays. *IEEE Transactions on Power Electronics*. 2009; 24(5): 1198,1208.

- [23] ZB Ibrahim, Md L Hossaion, IB Budis, JM Lazi, NM Yaakkop. Comparative analysis of PWM techniques for three level diode clamped voltage source inverter. *Int. Journal of Power Electronics and Drive System (IJPEDS)*. 2014; 5(1): 15-23.

- [24] OD Momoh. Modeling and simulation of a aarrier-based PWM voltage source inverter for a nine phase induction machine drive. *Int. Journal of Power Electronics and Drive System (IJPEDS)*. 2014; 5(1): 1-14.

- [25] ZB Ibrahim, Md L Hossain, IB Bugis, JM Lazi, NM Yaakop. Comparative analysis of PWM techniques for three level diode clamped voltage source inverter. *Int. Journal of Power Electronics and Drive System (IJPEDS)*. Special Issue on Electric Power Converter. 2014; 5: 15-23.

## **BIOGRAPHIES OF AUTHORS**

**Mostafa Barzegar Kalashani** was born in Salmas, Iran in February 1989. He received his B.Sc. degree in power electrical engineering from University of Urmia, Urmia, Iran, in 2012 and he is currently M.Sc. student in power electrical engineering in Urmia University, Urmia, Iran. His interest fields are mostly photovoltaic systems, multilevel inverters, Z-Source converters, application of power electronic converters to renewable energy systems.

Murtaza Farsadi was born in Khoy, Iran in September 1957. He received his B.Sc. degree in Electrical Engineering, M.Sc. degree in Electrical and Electronics Engineering and Ph.D. degree in Electrical Engineering (High Voltage) from Middle East Technical University (METU), Ankara, Turkey in 1982, 1984 and 1989, respectively. He is now an assistant professor in the Electrical Engineering Department of Urmia University, Urmia, Iran. His main research interests are in high voltage engineering, industrial power system studies and FACTS, HVDC transmission systems, DC/AC active power filters, renewable energy, hybrid and electrical vehicles, and new control methods.